IC Back-End of Line Project

This projects studies the thermal effects in the Back-End of line of integrated circuits (ICs) especially in large scale integration (VLSI and ULSI). The high electric current densities and the miniaturization trends lead to an increase in interconnect self-heating rates and elevated operation temperatures that would exacerbate electromigration effects in the power/ground (P/G) BEoL network. Since full scale simulations are extremely computationally expensive for vast networks of interconnects, a reduced thermal model is most preferable for a quick thermal check for reliability analysis. This work investigates the accuracy and validity of reduced 2D and 3D thermal models for interconnects and utilizes high-resolution thermal imaging and fast-computational capabilities to develop more accurate models. Other thermal effects are investigated in the BEoL, such as the cooling effect of the dummy metal fill used for the Chemical-Mechanical Planarization (CMP) process. The cooling effect is further exploited by designing a heat spreader to target thermally critical interconnects.

Compact Thermal Model for Reliability Characterization of Interconnect Power Network in the BEoL of ICs

Assaad El Helou, Archana Venugopal, and Peter E. Raad

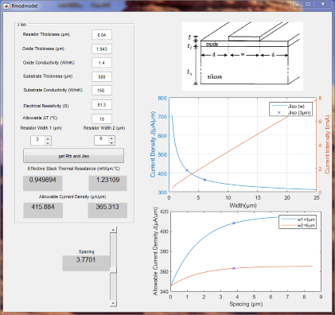

Mathematical and empirical models have been the fastest thermal characterization approach for interconnects embedded in a dielectric medium. In this study, the accuracy of these models are assessed, and a more accuracte model is developed and verified with numerical simulations and validated with experimental thermal maps.

Specially fabricated sample devices are thermally mapped to validate the reduced models and the thermal simulations. The structure of the samples are presented in the figures below and consist of microresistors acting as heat sources in different levels of the BEoL.

The experimental and numerical analysis is performed to assess the accuracy and validity of 2D reduced models and to improve upon them.

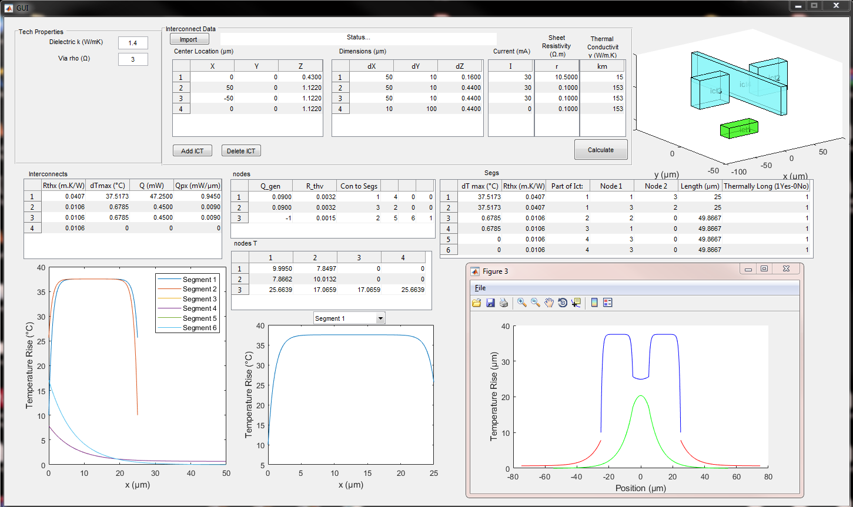

The 2D model is expanded to include 3D effects at the interconnect ends, as well as conduction to the vias and conduction in cross configurations. A lossy wire model is implemented with an iterative method to develop a thermal resistive network of heat conduction between the different interconnects. The conduction to the surrounding is governed by the 2D reduced thermal model presented earlier and can provide the maximum attainable temperature rise in the interconnect. The model is verified with numerical simulations and validated with experimental measurements of sample BEoL structures.

Thermal investigation of Cooling effect of CMP dummy fill in BEoL

Assaad El Helou, Archana Venugopal, and Peter E. Raad

The metallic dummy fill used in conjunction with the CMP process of IC fabrication has been observed to have a thermal cooling effect on the BEoL. The metallic material increases the effective conductance of the stack and thus can reduce the operating temperature within the BEoL and expand thermal activation limits. A numerical study is conducted to estimate the cooling potential of a square fill pattern on the activation limits of interconnect structures of different sizes and BEoL location. The structure of a 10 µm microresistor is shown below. The CMP pattern is seen around the device and an exclusion zone is used to provide optical access for thermal imaging validation.

Standardized Heat Spreader Design for Thermally Critical BEoL Interconnects

The observed cooling effect of the CMP dummy fill is then used to design a heat spreader for thermally critical interconnects at the Level 3 of the BEoL. The heat spreader is made of a traversely running metallic fins in Level 1 and Level 2 to enhace the heat spreading effect and reduce the operating temperature.

The test structures of the heat spreader are thermally mapped to observe the cooling effect at different power levels.

The thermal simulation model of the BEoL and the embedded HS is used for an additional parametric analysis where the cooling effect of the HS width is determined for the different interconnect configurations.

Other Projects

Back-End of Line

SMU-Texas Instruments

Investigating and mitigating self-heating in IC Back-End of Line (BEoL) interconnect networks.

High Power GaN HEMTs

SMU-Naval Research Lab

Combined experimental and numerical approach to fully thermally characterize the self-heating in high power GaN HEMTs.